多路数据选择器设计实验 实验源码及工程文件:https://github.com/Chaos-xBug/selector_4-1

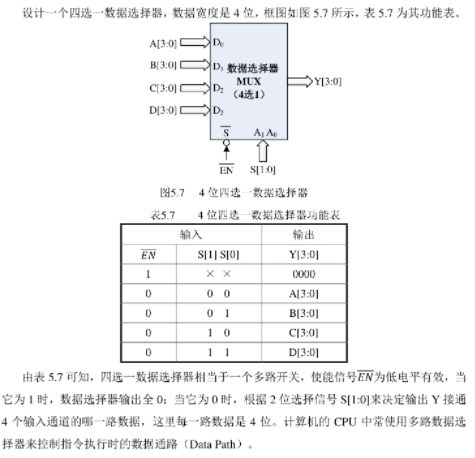

实验内容

具体实验 选择xc7a100tlcsg324-2L板卡型号

数据选择器模块 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 `timescale 1ns / 1ps module selector(A, B, C, D, EN, S, Y); parameter size = 4 ; input [size-1 :0 ]A; input [size-1 :0 ]B; input [size-1 :0 ]C; input [size-1 :0 ]D; input EN; input [1 :0 ]S; output reg [size-1 :0 ]Y; always @(A, B, C, D, EN, S) begin if (EN == 0 ) begin case (S) 2'b00 : Y = A; 2'b01 : Y = B; 2'b10 : Y = C; 2'b11 : Y = D; endcase end else Y = 4'b0000 ; end endmodule

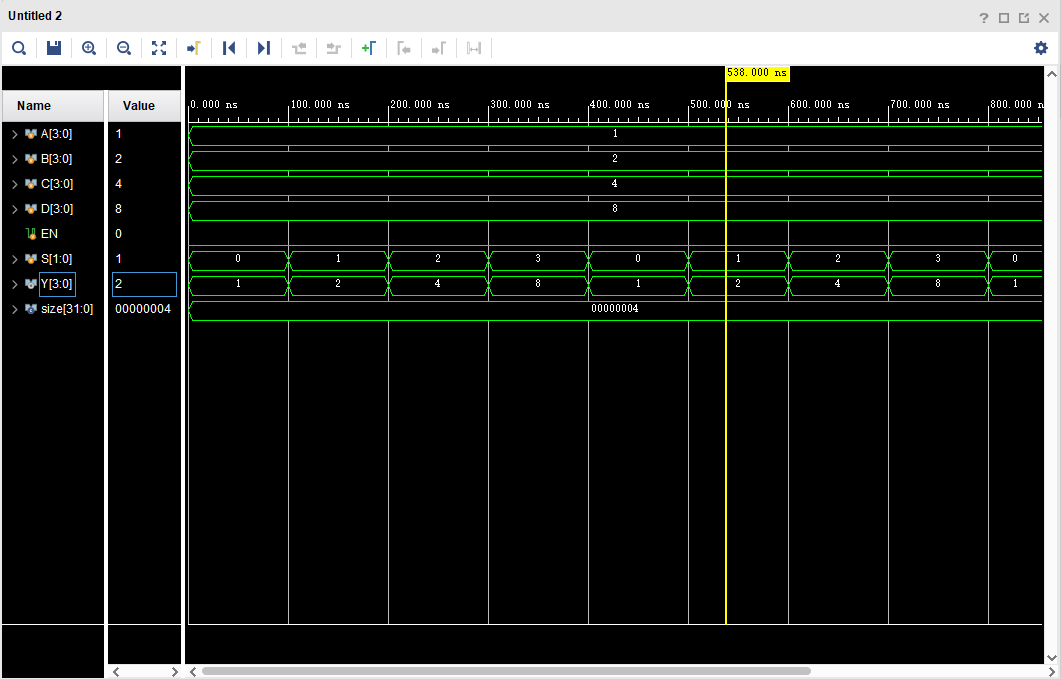

仿真代码 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 `timescale 1ns / 1ps module tb_selector; parameter size = 4 ;reg [size-1 :0 ] A = 0 ;reg [size-1 :0 ] B = 0 ;reg [size-1 :0 ] C = 0 ;reg [size-1 :0 ] D = 0 ;reg EN = 0 ;reg [1 :0 ] S = 0 ;wire [size-1 :0 ] Y ;selector #( .size ( size )) u_selector ( .A ( A [size-1 :0 ] ), .B ( B [size-1 :0 ] ), .C ( C [size-1 :0 ] ), .D ( D [size-1 :0 ] ), .EN ( EN ), .S ( S [1 :0 ] ), .Y ( Y [size-1 :0 ] ) ); initial begin A = 4'b0001 ; B = 4'b0010 ; C = 4'b0100 ; D = 4'b1000 ; EN = 0 ; S = 2'b00 ; end always begin #100 S = S + 2'b01 ; end endmodule

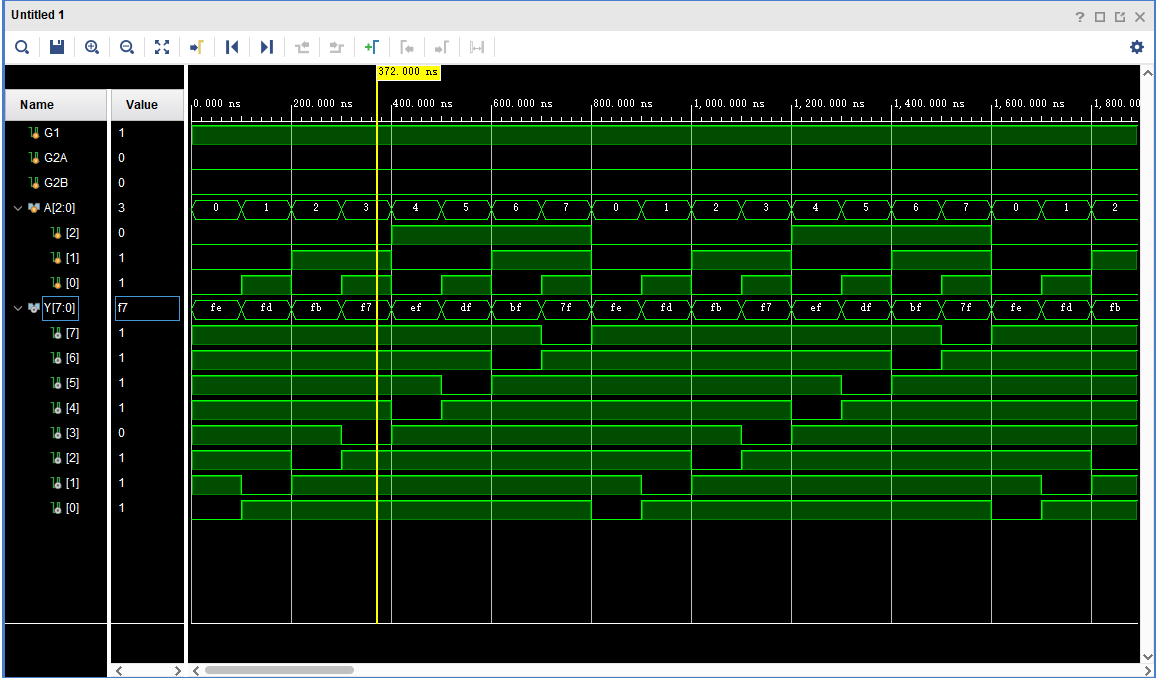

仿真结果

板极验证 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 set_property IOSTANDARD LVCMOS18 [get_ports {A[3]}] set_property IOSTANDARD LVCMOS18 [get_ports {A[2]}] set_property IOSTANDARD LVCMOS18 [get_ports {A[1]}] set_property IOSTANDARD LVCMOS18 [get_ports {A[0]}] set_property IOSTANDARD LVCMOS18 [get_ports {B[3]}] set_property IOSTANDARD LVCMOS18 [get_ports {B[2]}] set_property IOSTANDARD LVCMOS18 [get_ports {B[1]}] set_property IOSTANDARD LVCMOS18 [get_ports {B[0]}] set_property IOSTANDARD LVCMOS18 [get_ports {C[3]}] set_property IOSTANDARD LVCMOS18 [get_ports {C[2]}] set_property IOSTANDARD LVCMOS18 [get_ports {C[1]}] set_property IOSTANDARD LVCMOS18 [get_ports {C[0]}] set_property IOSTANDARD LVCMOS18 [get_ports {D[3]}] set_property IOSTANDARD LVCMOS18 [get_ports {D[2]}] set_property IOSTANDARD LVCMOS18 [get_ports {D[1]}] set_property IOSTANDARD LVCMOS18 [get_ports {D[0]}] set_property IOSTANDARD LVCMOS18 [get_ports {S[1]}] set_property IOSTANDARD LVCMOS18 [get_ports {S[0]}] set_property IOSTANDARD LVCMOS18 [get_ports {Y[3]}] set_property IOSTANDARD LVCMOS18 [get_ports {Y[2]}] set_property IOSTANDARD LVCMOS18 [get_ports {Y[1]}] set_property IOSTANDARD LVCMOS18 [get_ports {Y[0]}] set_property IOSTANDARD LVCMOS18 [get_ports EN] set_property PACKAGE_PIN V5 [get_ports {A[3]}] set_property PACKAGE_PIN T4 [get_ports {A[2]}] set_property PACKAGE_PIN V6 [get_ports {A[1]}] set_property PACKAGE_PIN T5 [get_ports {A[0]}] set_property PACKAGE_PIN T6 [get_ports {B[3]}] set_property PACKAGE_PIN V7 [get_ports {B[2]}] set_property PACKAGE_PIN R8 [get_ports {B[1]}] set_property PACKAGE_PIN U9 [get_ports {B[0]}] set_property PACKAGE_PIN T9 [get_ports {C[3]}] set_property PACKAGE_PIN V10 [get_ports {C[2]}] set_property PACKAGE_PIN R10 [get_ports {C[1]}] set_property PACKAGE_PIN U11 [get_ports {C[0]}] set_property PACKAGE_PIN R11 [get_ports {D[3]}] set_property PACKAGE_PIN U12 [get_ports {D[2]}] set_property PACKAGE_PIN T13 [get_ports {D[1]}] set_property PACKAGE_PIN V14 [get_ports {D[0]}] set_property PACKAGE_PIN T14 [get_ports EN] set_property PACKAGE_PIN V15 [get_ports {S[1]}] set_property PACKAGE_PIN R15 [get_ports {S[0]}] set_property PACKAGE_PIN U6 [get_ports {Y[3]}] set_property PACKAGE_PIN R5 [get_ports {Y[2]}] set_property PACKAGE_PIN U7 [get_ports {Y[1]}] set_property PACKAGE_PIN R6 [get_ports {Y[0]}]