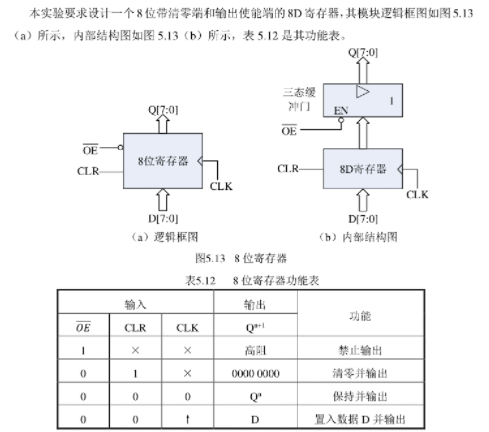

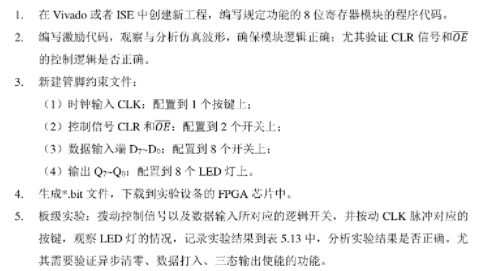

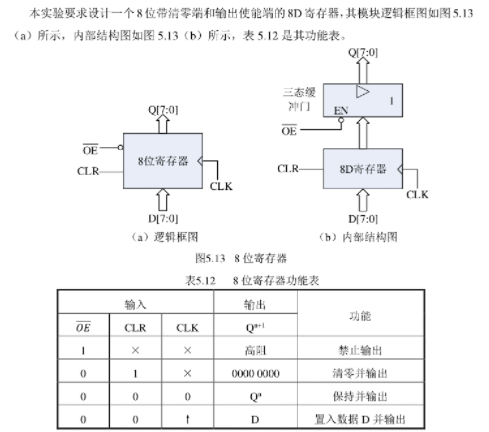

基本寄存器设计实验

实验原理

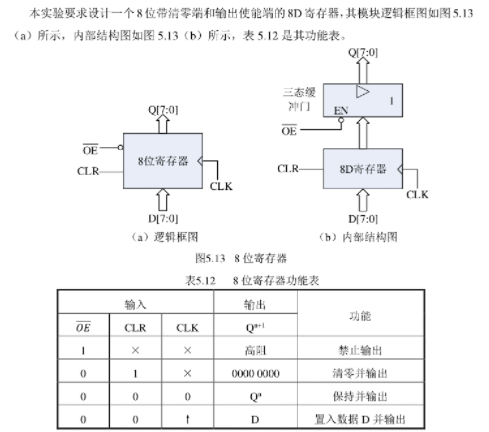

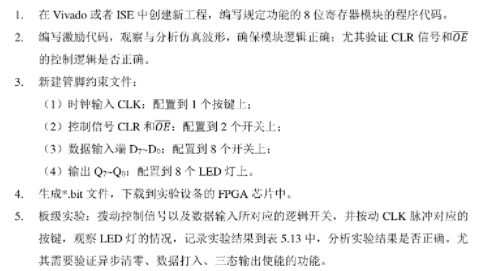

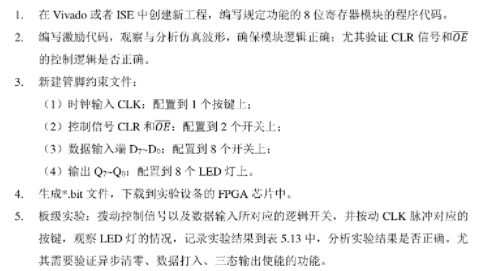

实验步骤

实验代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

| `timescale 1ns / 1ps

module register_8D(OE_, CLR, CLK, D, Q);

input OE_, CLR, CLK;

input [7:0]D;

output [7:0]Q;

reg [7:0]A;

always @(posedge CLK or posedge CLR) begin

if(CLR) A <= 8'b0000_0000;

else A <= D;

end

assign Q = OE_ ? 8'bzzzz_zzzz : A;

endmodule

|

板极验证

使用的板卡型号:xc7a100tlcsg324-2L

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

| set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN V5} [get_ports OE_]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets CLR]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN T4} [get_ports CLR]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets CLK]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U17} [get_ports CLK]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN R11} [get_ports {D[7]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U12} [get_ports {D[6]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN T13} [get_ports {D[5]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN V14} [get_ports {D[4]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN T14} [get_ports {D[3]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN V15} [get_ports {D[2]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN R15} [get_ports {D[1]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U16} [get_ports {D[0]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U6} [get_ports {Q[7]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN R5} [get_ports {Q[6]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U7} [get_ports {Q[5]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN R6} [get_ports {Q[4]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN R7} [get_ports {Q[3]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN U8} [get_ports {Q[2]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN T8} [get_ports {Q[1]}]

set_property -dict {IOSTANDARD LVCMOS18 PACKAGE_PIN V9} [get_ports {Q[0]}]

|